Page 688 - 완) I MDP 프로젝트 작품 보고서(전체과 1학년)1.6

P. 688

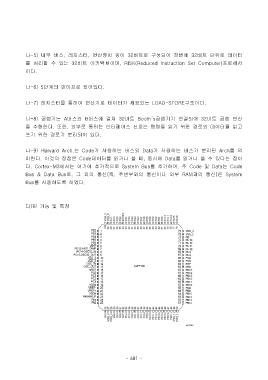

나-5) 내부 버스, 레지스터, 연산장치 등이 32비트로 구성되어 한번에 32비트 단위로 데이터

를 처리할 수 있는 32비트 아키텍쳐이며, RISK(Reduced Instruction Set Computer)프로세서

이다.

나-6) 5단계의 파이프로 되어있다.

나-7) 레지스터를 통하여 연산기로 데이터가 제공되는 LOAD-STORE구조이다.

나-8) 곱셈기는 A버스와 B버스에 걸쳐 32비트 Booth’s곱셈기가 연결되어 32비트 곱셈 연산

을 수행한다. 또한, 외부로 통하는 인터페이스 신호는 명령을 읽기 위한 경로와 데이터를 읽고

쓰기 위한 경로가 분리되어 있다.

나-9) Harvard Arch.는 Code가 사용하는 버스와 Data가 사용하는 버스가 분리된 Arch를 의

미한다. 이것의 장점은 Code데이터를 읽거나 쓸 때, 동시에 Data를 읽거나 쓸 수 있다는 점이

다. Cortex-M3에서는 여기에 추가적으로 System Bus를 추가하여, 주 Code 및 Data는 Code

Bus & Data Bus로, 그 외의 통신(즉, 주변부와의 통신이나 외부 RAM과의 통신)은 System

Bus를 사용하도록 하였다.

다)핀 기능 및 특징

- 681 -