Page 204 - 완) I MDP 프로젝트 작품 보고서(전체과 1학년)1.6

P. 204

3. 특수 레지스터

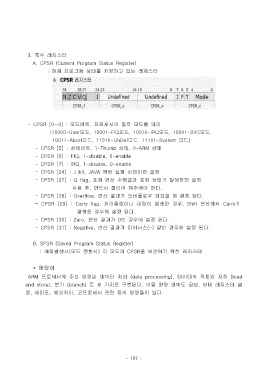

A. CPSR (Current Program Status Register)

: 현재 프로그램 상태를 저장하고 있는 레지스터

- CPSR [0~4] : 모드비트, 프로세서의 동작 모드를 의미

(10000-User모드, 10001-FIQ모드, 10010-IRQ모드, 10011-SVC모드,

10011-Abort모드, 11011-UnDef모드, 11111-System 모드)

- CPSR [5] : 상태비트, 1-Thumb 상태, 0-ARM 상태

- CPSR [6] : FIQ, 1-disable, 0-enable

- CPSR [7] : IRQ, 1-disable, 0-enable

- CPSR [24] : J bit, JAVA 명령 실행 상태이면 설정

- CPSR [27] : Q flag, 포화 연산 수행결과 포화 상태가 발생하면 설정

사용 후, 반드시 클리어 해주어야 한다.

- CPSR [28] : Overflow, 연산 결과가 오버플로우 되었을 때 설정 된다.

- CPSR [29] : Carry flag, 자리올림이나 내림이 발생한 경우, Shift 연산에서 Carry가

발생한 경우에 설정 된다.

- CPSR [30] : Zero, 연산 결과가 0인 경우에 설정 된다.

- CPSR [31] : Negative, 연산 결과가 마이너스(-) 값인 경우에 설정 된다.

B. SPSR (Saved Program Status Register)

: 예외발생시(모드 전환시) 각 모드의 CPSR을 보관하기 위한 레지스터

* 명령어

ARM 프로세서의 주요 명령은 데이터 처리 (data processing), 데이터의 적재와 저장 (load

and store), 분기 (branch) 등 세 가지로 구분된다. 이들 명령 외에도 곱셈, 상태 레지스터 설

정, 세마포, 예외처리, 코프로세서 관련 등의 명령들이 있다.

- 197 -