Page 145 - 3-2

P. 145

end

else

begin

clk_cnt<=32'b0;

sec5_end<=1'b0;

end

end

end

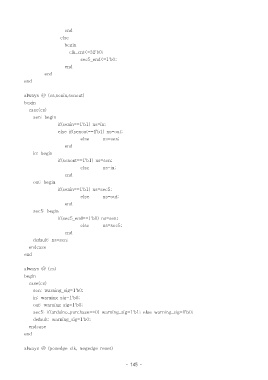

always @ (cs,senin,senout)

begin

case(cs)

sen: begin

if(senin==1'b1) ns=in;

else if(senout==1'b1) ns=out;

else ns=sen;

end

in: begin

if(senout==1'b1) ns=sen;

else ns=in;

end

out: begin

if(senin==1'b1) ns=sec5;

else ns=out;

end

sec5: begin

if(sec5_end==1'b1) ns=sen;

else ns=sec5;

end

default: ns=sen;

endcase

end

always @ (cs)

begin

case(cs)

sen: warning_sig=1'b0;

in: warning_sig=1'b0;

out: warning_sig=1'b0;

sec5: if(arduino_purchase==0) warning_sig=1'b1; else warning_sig=1'b0;

default: warning_sig=1'b0;

endcase

end

always @ (posedge clk, negedge reset)

- 145 -