Page 40 - 완) I MDP 프로젝트 작품 보고서(전체과 1학년)1.6

P. 40

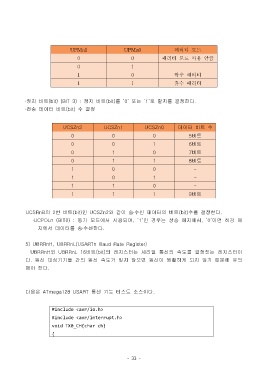

․정지 비트(bit) (BIT 3) : 정지 비트(bit)를 ‘0’ 또는 ‘1’로 할지를 결정한다.

․전송 데이터 비트(bit) 수 결정

UCSZn2 UCSZn1 UCSZn0 데이터 비트 수

0 0 0 5비트

0 0 1 6비트

0 1 0 7비트

0 1 1 8비트

1 0 0 -

1 0 1 -

1 1 0 -

1 1 1 9비트

UCSRnB의 2번 비트(bit)인 UCSZn2와 같이 송․수신 데이터의 비트(bit)수를 결정한다.

․UCPOLn (BIT0) : 동기 모드에서 사용되며, ‘1’인 경우는 상승 에지에서, ‘0’이면 하강 에

지에서 데이터를 송․수신한다.

5) UBRRnH, UBRRnL(USARTn Baud Rate Register)

UBRRnH와 UBRRnL 16비트(bit)의 레지스터는 시리얼 통신의 속도를 결정짓는 레지스터이

다. 통신 대상기기들 간의 통신 속도가 맞지 않으면 통신이 원활하게 되지 않기 때문에 유의

해야 한다.

다음은 ATmega128 USART 통신 기능 테스트 소스이다.

#include <avr/io.h>

#include <avr/interrupt.h>

void TX0_CH(char ch)

{

- 33 -