Page 18 - 완) I MDP 프로젝트 작품 보고서(전체과 1학년)1.6

P. 18

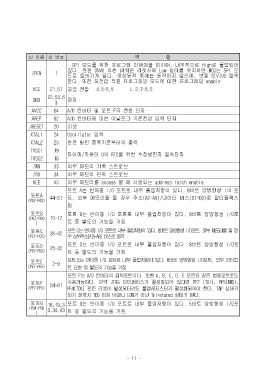

핀 이름 핀 번호 역 할

SPI 모드를 위한 프로그램 인에이블 핀이며, 내부적으로 High로 풀업되어

있다. 전원 ON에 의한 파워온 리셋시에 Low 상태를 유지하면 MCU는 SPI 모

/PEN 1

드로 들어가게 된다. 정상동작 중에는 동작하지 않으며, 보통 5[V]에 접속

한다. 또한 저전압 직렬 프로그래밍 모드에 대한 프로그래밍 enable

VCC 21,51 공급 전압 4.5~5.5 L 2.7~5.5

22,53,6

GND 접지

3

AVCC 64 A/D 컨버터 및 포트 F의 전원 단자

AREF 62 A/D 컨버터에 대한 아날로그 기준전압 입력 단자

/RESET 20 리셋

XTAL1 24 Oscillator 입력

XTAL2 23 반전 발진 증폭기로부터의 출력

TOSC1 19

타이머/카운터 O의 RTC를 위한 수정발진자 접속단자

TOSC2 18

/WR 33 외부 메모리 기록 스트로브

/RD 34 외부 메모리 판독 스트로브

ALE 43 외부 메모리를 access 할 때 사용되는 address latch enable

포트 A는 반이중 I/O 포트로 내부 풀업저항이 있다. 8비트 양방향성 I/O 포

포트A

(PA7~PA0) 44~51 트, 외부 메모리를 둘 경우 주소(A7~A0)/데이터 버스(D7~D0)로 멀티플렉스

됨

포트B 포트 B는 반이중 I/O 포트로 내부 풀업저항이 있다. 8비트 양방향성 I/O포

(PB7~PB0 10~17

) 트 등 별도의 기능을 가짐

포트C 35~42 포트 C는 반이중 I/O 포트로 내부 풀업저항이 있다. 8비트 양방향성 I/O포트, 외부 메모리를 둘 경

(PC7~PC0) 우 상위주소(A15~A8) 버스로 동작

포트D 25~32 포트 D는 반이중 I/O 포트로 내부 풀업저항이 있다. 8비트 양방향성 I/O포

(PD7~PD0) 트 등 별도의 기능을 가짐

포트E 2~9 포트 E는 반이중 I/O 포트로 내부 풀업저항이 있다. 8비트 양방향성 I/O포트, 외부 인터럽

(PE7~PE0) 트 요청 등 별도의 기능을 가짐

포트 F는 A/D 컨버터의 입력포트이다. 또한 A, B, C, D, E 포트와 같은 범용포트로도

포트F 54~61 사용가능하다. 만약 JTAG 인터페이스가 활성화되어 있다면 PF7 (TDI), PF5(TMS),

(PF7~PF0) PF4(TCK) 핀은 리셋이 발생되더라도 풀업레지스터가 활성화되어야 한다. TAP 상태가

되기 전까지 TDO 핀은 HIGH나 LOW가 아닌 Tri-stated 상태가 된다.

포트G 18,19,3 포트 G는 반이중 I/O 포트로 내부 풀업저항이 있다. 5비트 양방향성 I/O포

(PG4~PG0 3,34,43

) 트 등 별도의 기능을 가짐

- 11 -