Page 505 - 완) I MDP 프로젝트 작품 보고서(전체과 1학년)1.6

P. 505

인천전자마이스터고 전자회로설계과

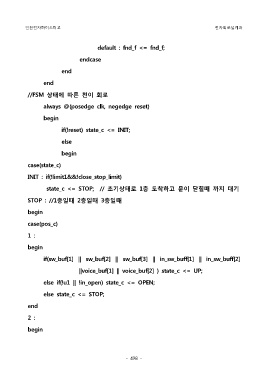

default : fnd_f <= fnd_f;

endcase

end

end

//FSM 상태에 따른 천이 회로

always @(posedge clk, negedge reset)

begin

if(!reset) state_c <= INIT;

else

begin

case(state_c)

INIT : if(!limit1&&!close_stop_limit)

state_c <= STOP; // 초기상태로 1층 도착하고 문이 닫힐때 까지 대기

STOP : //1층일때 2층일때 3층일때

begin

case(pos_c)

1 :

begin

if(sw_buf[1] || sw_buf[2] || sw_buf[3] || in_sw_buff[1] || in_sw_buff[2]

||voice_buf[1] || voice_buf[2] ) state_c <= UP;

else if(!u1 || !in_open) state_c <= OPEN;

else state_c <= STOP;

end

2 :

begin

- 498 -