Page 692 - 3-2

P. 692

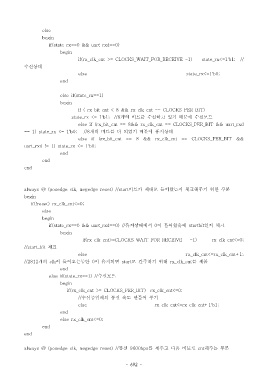

else

begin

if(state_rx==0 && uart_rxd==0)

begin

if(rx_clk_cnt >= CLOCKS_WAIT_FOR_RECEIVE -1) state_rx<=1'b1; //

수신상태

else state_rx<=1'b0;

end

else if(state_rx==1)

begin

if ( rx_bit_cnt < 8 && rx_clk_cnt == CLOCKS_PER_BIT)

state_rx <= 1'b1; //8 개의 비트를 수신하고 있기 때문에 수신모드

else if (rx_bit_cnt == 8&& rx_clk_cnt == CLOCKS_PER_BIT && uart_rxd

== 1) state_rx <= 1'b0; //8 개의 비트를 다 되었기 때문에 휴지상태

else if (rx_bit_cnt == 8 && rx_clk_cnt == CLOCKS_PER_BIT &&

uart_rxd != 1) state_rx <= 1'b0;

end

end

end

always @ (posedge clk, negedge reset) //start 비트가 제대로 들어왔는지 체크해주기 위한 부분

begin

if(!reset) rx_clk_cnt<=0;

else

begin

if(state_rx==0 && uart_rxd==0) // 휴지상태에서 0 이 들어왔을때 startbit 인지 체크

begin

if(rx_clk_cnt>=CLOCKS_WAIT_FOR_RECEIVE -1) rx_clk_cnt<=0;

//start_bit 체크

else rx_clk_cnt<=rx_clk_cnt+1;

//2812 개의 clk 이 들어오는동안 0 이 유지되면 start 로 간주하기 위해 rx_clk_cnt 를 세줌

end

else if(state_rx==1) // 수신모드

begin

if(rx_clk_cnt >= CLOCKS_PER_BIT) rx_clk_cnt<=0;

// 수신중일때의 통신 속도 만들어 주기

else rx_clk_cnt<=rx_clk_cnt+1'b1;

end

else rx_clk_cnt<=0;

end

end

always @ (posedge clk, negedge reset) // 통신 9600bps 를 세주고 다음 비트로 cnt 해주는 부분

- 692 -