Page 429 - 3-3

P. 429

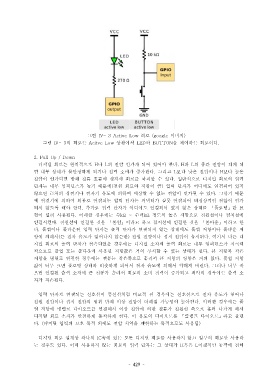

그림 Ⅳ - 3 Active Low 회로 (google 이미지)

그림 Ⅳ - 3 의 회로는 Acitve Low 상황에서 LED 와 BUTTON 을 제어하는 회로이다.

2. Pull Up / Down

디지털 회로는 원칙적으로 H 나 L 의 전압 인가가 되어 있어야 한다. H 와 L 의 중간 전압이 되게 되

면 내부 상태가 불안정하게 되거나 전력 소비가 증가한다 그리고. L 보다 낮은 전압이나 H 보다 높은

전압이 인가되면 방해 전류 흐름이 생겨서 회로를 파괴할 수 있다 일반적으로 디지털 회로의 입력.

단자는 내부 임피던스가 높기 때문에 전원 회로와 저항이 큼 입력 단자가 어디에도 연결되어 있지( )

않으면 근처의 정전기나 전자기 유도에 의하여 예상할 수 없는 전압이 인가될 수 있다 그렇기 때문.

에 연결기에 의하여 외부로 연결되는 입력 단자는 커넥터가 잘못 연결되어 비정상적인 전압이 인가

되지 않도록 해야 한다 추가로 입력 단자가 어디에도 연결되어 있지 않은 상태를. 「 플로팅 란 표」

현이 널리 사용된다 이러한 경우에는 수. kΩ ~ 수백kΩ 정도의 높은 저항으로 전원선이나 접지선에

연결시킨다 전원선에 연결한 것을. 「 풀업 이라고 하고 접지선에 연결한 것을」 「 풀다운」 이라고 한

다 풀업이나 풀다운된 입력 단자는 출력 단자가 연결되지 않는 상태에도 풀업 저항이나 풀다운 저.

항에 의해서 큰 전자 유도가 일어나지 않는한 전원 전압이나 접지 전압이 유지된다 여기서 다른 디( ) .

지털 회로의 출력 단자가 접속되었을 경우에는 디지털 소자의 출력 회로는 내부 임피던스가 지극히

작으므로 풀업 또는 풀다운에 사용된 저항값은 거의 무시할 수 있는 상태가 된다 큰 저항과 작은.

저항을 병렬로 연결한 경우에는 전류는 작은쪽으로 흘러서 큰 저항의 영향은 거의 없다 풀업 저항.

값이 너무 크면 플로팅 상태와 비슷하게 되어서 전자 유도에 의해서 약해져 버린다 그러나 너무 작.

으면 연결된 출력 소자에 큰 전류가 흘러서 회로의 소비 전력이 증가되고 최악의 경우에는 출력 소

자가 파손된다.

입력 단자로 연결되는 신호선이 통신선처럼 비교적 길 경우에는 신호선으로 전자 유도가 일어나

전원 전압이나 접지 전압의 범위 밖의 이상 전압이 더해질 가능성이 높아진다 이러한 경우에는 풀.

업 저항에 병렬로 다이오드를 연결해서 이상 전압에 의한 전류가 전원선 쪽으로 흘러 나가게 해서

디지털 회로 소자가 안전하게 동작하게 한다 이 용도의 다이오드를. 「 클램프 다이오드 라고 불린」

다. ( 디지털 입력의 보호 목적 외에도 전압 치역을 제한하는 목적으로도 사용됨)

디지털 회로 설계상 하나의 IC 속에 있는 모든 디지털 회로를 사용하지 않고 일부의 회로만 사용하

는 경우도 있다 이때 사용하지 않는 회로의 입력 단자는 그 상태가. H 혹은 L 이겠지만 동작에 전혀

- 429 -