Page 193 - MDP2020-2

P. 193

················································································ 명장양성프로젝트 【MDP】 과제발표회 자료집 Ⅱ | 187

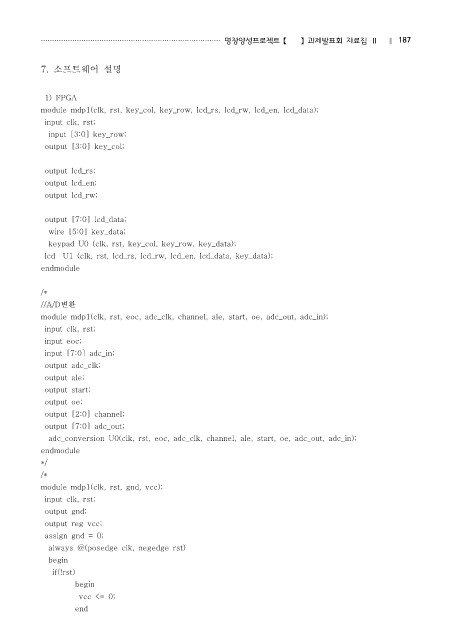

7. 소프트웨어 설명

1) FPGA

module mdp1(clk, rst, key_col, key_row, lcd_rs, lcd_rw, lcd_en, lcd_data);

input clk, rst;

input [3:0] key_row;

output [3:0] key_col;

output lcd_rs;

output lcd_en;

output lcd_rw;

output [7:0] lcd_data;

wire [5:0] key_data;

keypad U0 (clk, rst, key_col, key_row, key_data);

lcd U1 (clk, rst, lcd_rs, lcd_rw, lcd_en, lcd_data, key_data);

endmodule

/*

//A/D변환

module mdp1(clk, rst, eoc, adc_clk, channel, ale, start, oe, adc_out, adc_in);

input clk, rst;

input eoc;

input [7:0] adc_in;

output adc_clk;

output ale;

output start;

output oe;

output [2:0] channel;

output [7:0] adc_out;

adc_conversion U0(clk, rst, eoc, adc_clk, channel, ale, start, oe, adc_out, adc_in);

endmodule

*/

/*

module mdp1(clk, rst, gnd, vcc);

input clk, rst;

output gnd;

output reg vcc;

assign gnd = 0;

always @(posedge clk, negedge rst)

begin

if(!rst)

begin

vcc <= 0;

end