Page 1110 - 3-2

P. 1110

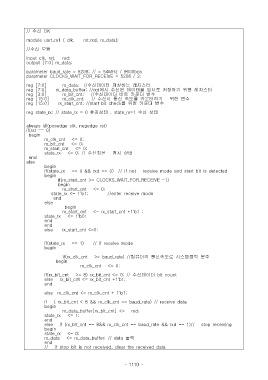

// 수신 OK

module uart_rx1 ( clk, rst,rxd, rx_data);

// 수신 모듈

input clk, rst, rxd;

output [7:0] rx_data;

parameter baud_rate = 5208; // = 54MHz / 9600bps

parameter CLOCKS_WAIT_FOR_RECEIVE = 5208 / 2;

reg [7:0] rx_data; // 수신데이터 저장하는 레지스터

reg [7:0] rx_data_buffer; //rxd 에서 수신된 데이터를 임시로 저장하기 위한 레지스터

reg [3:0] rx_bit_cnt; // 수신데이터 비트 카운터 변수

reg [15:0] rx_clk_cnt; // 수신시 통신 속도를 카운터하기 위한 변수

reg [15:0] rx_start_cnt; //start bit check 를 위한 카운터 변수

reg state_rx; // state_rx = 0 휴지상태 , state_rx=1 수신 상태

always @(posedge clk, negedge rst)

if(rst == 0)

begin

rx_clk_cnt <= 0;

rx_bit_cnt <= 0;

rx_start_cnt <= 0;

state_rx <= 0; // 수신회선 휴지 상태

end

else

begin

if(state_rx == 0 && rxd == 0) // if not receive mode and start bit is detected

begin

if(rx_start_cnt >= CLOCKS_WAIT_FOR_RECEIVE -1)

begin

rx_start_cnt <= 0;

state_rx <= 1'b1; //enter receive mode

end

else

begin

rx_start_cnt <= rx_start_cnt +1'b1 ;

state_rx <= 1'b0;

end

end

else rx_start_cnt <=0;

if(state_rx == 1) // if receive mode

begin

if(rx_clk_cnt >= baud_rate) // 컴퓨터의 통신속도로 시스템클럭 분주

begin

rx_clk_cnt <= 0;

if(rx_bit_cnt >= 8) rx_bit_cnt <= 0; // 수신데이터 bit count

else rx_bit_cnt <= rx_bit_cnt +1'b1;

end

else rx_clk_cnt <= rx_clk_cnt + 1'b1;

if ( rx_bit_cnt < 8 && rx_clk_cnt == baud_rate) // receive data

begin

rx_data_buffer[rx_bit_cnt] <= rxd;

state_rx <= 1;

end

else if (rx_bit_cnt == 8&& rx_clk_cnt == baud_rate && rxd == 1)// stop receiving

begin

state_rx <= 0;

rx_data <= rx_data_buffer; // data 출력

end

// if stop bit is not received, clear the received data

- 1110 -