Page 725 - 완) I MDP 프로젝트 작품 보고서(전체과 1학년)1.6

P. 725

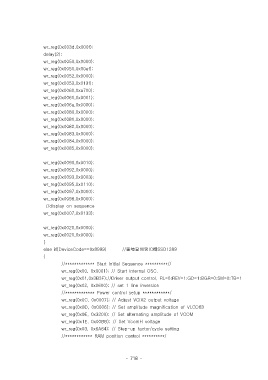

wr_reg(0x003d,0x000f);

delay(2);

wr_reg(0x0050,0x0000);

wr_reg(0x0051,0x00ef);

wr_reg(0x0052,0x0000);

wr_reg(0x0053,0x013f);

wr_reg(0x0060,0xa700);

wr_reg(0x0061,0x0001);

wr_reg(0x006a,0x0000);

wr_reg(0x0080,0x0000);

wr_reg(0x0081,0x0000);

wr_reg(0x0082,0x0000);

wr_reg(0x0083,0x0000);

wr_reg(0x0084,0x0000);

wr_reg(0x0085,0x0000);

wr_reg(0x0090,0x0010);

wr_reg(0x0092,0x0000);

wr_reg(0x0093,0x0003);

wr_reg(0x0095,0x0110);

wr_reg(0x0097,0x0000);

wr_reg(0x0098,0x0000);

//display on sequence

wr_reg(0x0007,0x0133);

wr_reg(0x0020,0x0000);

wr_reg(0x0021,0x0000);

}

else if(DeviceCode==0x8999) //뚤壇돨혜땡IC槨SSD1289

{

//************* Start Initial Sequence **********//

wr_reg(0x00, 0x0001); // Start internal OSC.

wr_reg(0x01,0x3B3F);//Driver output control, RL=0;REV=1;GD=1;BGR=0;SM=0;TB=1

wr_reg(0x02, 0x0600); // set 1 line inversion

//************* Power control setup ************/

wr_reg(0x0C, 0x0007); // Adjust VCIX2 output voltage

wr_reg(0x0D, 0x0006); // Set amplitude magnification of VLCD63

wr_reg(0x0E, 0x3200); // Set alternating amplitude of VCOM

wr_reg(0x1E, 0x00BB); // Set VcomH voltage

wr_reg(0x03, 0x6A64); // Step-up factor/cycle setting

//************ RAM position control **********/

- 718 -