Page 360 - 완) I MDP 프로젝트 작품 보고서(전체과 1학년)1.6

P. 360

정보통신기기 프로젝트

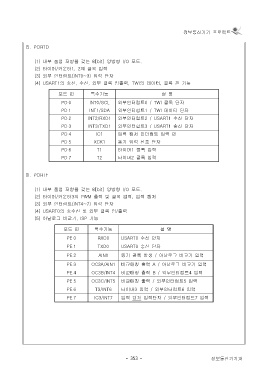

라. PORTD

(1) 내부 풀업 저항을 갖는 8[bit] 양방향 I/O 포트.

(2) 타이머/카운터1, 2의 클록 입력

(3) 외부 인터럽트(INT0~3) 입력 단자

(4) USART1의 송신, 수신, 외부 클록 입출력, TWI의 데이터, 클록 핀 기능

포트 핀 특수기능 설 명

PD 0 INT0/SCL 외부인터럽트0 / TWI 클록 단자

PD 1 INT1/SDA 외부인터럽트1 / TWI 데이터 단자

PD 2 INT2/RXD1 외부인터럽트2 / USART1 수신 단자

PD 3 INT3/TXD1 외부인터럽트3 / USART1 송신 단자

PD 4 IC1 입력 캡처 인터럽트 입력 핀

PD 5 XCK1 동기 입력 신호 단자

PD 6 T1 타이머1 클록 입력

PD 7 T2 타이머2 클록 입력

마. PORTE

(1) 내부 풀업 저항을 갖는 8[bit] 양방향 I/O 포트.

(2) 타이머/카운터3의 PWM 출력 및 클록 입력, 입력 캡처

(3) 외부 인터럽트(INT4~7) 입력 단자

(4) USART0의 송수신 및 외부 클록 입/출력

(5) 아날로그 비교기, ISP 기능

포트 핀 특수기능 설 명

PE 0 RXD0 USART0 수신 단자

PE 1 TXD0 USART0 송신 단자

PE 2 AIN0 동기 클록 발생 / 아날로그 비교기 입력

PE 3 OC3A/AIN1 비교매칭 출력 A / 아날로그 비교기 입력

PE 4 OC3B/INT4 비교매칭 출력 B / 외부인터럽트4 입력

PE 5 OC3C/INT5 비교매칭 출력 / 외부인터럽트5 입력

PE 6 T3/INT6 타이머3 입력 / 외부인터럽트6 입력

PE 7 IC3/INT7 입력 캡처 입력단자 / 외부인터럽트7 입력

- 353 - 정보통신기기과