Page 433 - 2

P. 433

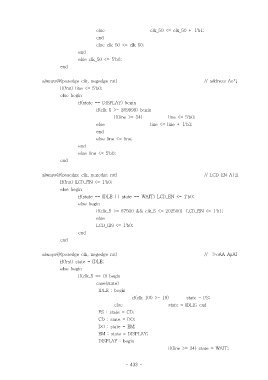

else clk_50 <= clk_50 + 1'b1;

end

else clk_50 <= clk_50;

end

else clk_50 <= 5'b0;

end

always@(posedge clk, negedge rst) // address Ao°¡

if(!rst) line <= 5'b0;

else begin

if(state == DISPLAY) begin

if(clk_5 >= 269999) begin

if(line >= 34) line <= 5'b0;

else line <= line + 1'b1;

end

else line <= line;

end

else line <= 5'b0;

end

always@(posedge clk, negedge rst) // LCD_EN A|¾i

if(!rst) LCD_EN <= 1'b0;

else begin

if(state == IDLE || state == WAIT) LCD_EN <= 1'b0;

else begin

if(clk_5 >= 67500 && clk_5 <= 202500) LCD_EN <= 1'b1;

else

LCD_EN <= 1'b0;

end

end

always@(posedge clk, negedge rst) // ≫ oAA A AIμ

if(!rst) state = IDLE;

else begin

if(clk_5 == 0) begin

case(state)

IDLE : begin

if(clk_100 >= 19) state = FS;

else state = IDLE; end

FS : state = CD;

CD : state = DO;

DO : state = EM;

EM : state = DISPLAY;

DISPLAY : begin

if(line >= 34) state = WAIT;

- 433 -