Page 1058 - 3-3

P. 1058

나 완전 이중방식) (Full-Duplex)

다 동기 및 비동기 전송 가능)

라 멀티프로세서 통신 모드로 동작 가능)

마 높은 정밀도의) Baud Rate 발생기 내장

바 인터럽트)

(1) 송신 완료 (Tx Complete)

(2) 송신 데이터 레지스터 준비완료 (Tx Data Register Empty)

(3) 수신 완료 (Rx Complete)

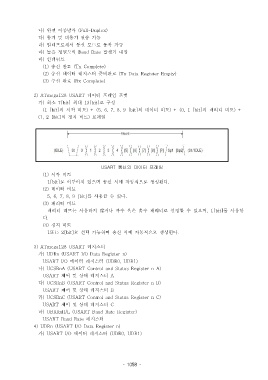

2) ATmega128 USART 데이터 프레임 포맷

가 최소) 7[bit] 최대 13[bit] 로 구성

(1 [bit] 의 시작 비트) + (5, 6, 7, 8, 9 [bit] 의 데이터 비트) + (0, 1 [bit] 의 패리티 비트) +

(1, 2 [bit] 의 정지 비트 프레임)

USART 통신의 데이터 프레임

(1) 시작 비트

1[bit] 로 이루어져 있으며 송신 시에 자동적으로 생성된다.

(2) 데이터 비트

5, 6, 7, 8, 9 [bit] 를 사용할 수 있다.

(3) 패리티 비트

패리티 비트는 사용하지 않거나 짝수 혹은 홀수 패리티로 설정할 수 있으며, 1[bit] 를 사용한

다.

(4) 정지 비트

1 또는 2[bit] 로 선택 가능하며 송신 시에 자동적으로 생성된다.

3) ATmega128 USART 레지스터

가) UDRn (USART I/O Data Register n)

USART I/O 데이터 레지스터 (UDR0, UDR1)

나) UCSRnA (USART Control and Status Register n A)

USART 제어 및 상태 레지스터 A

다) UCSRnB (USART Control and Status Register n B)

USART 제어 및 상태 레지스터 B

라) UCSRnC (USART Control and Status Register n C)

USART 제어 및 상태 레지스터 C

마) UBRRnH/L (USART Baud Rate Register)

USART Baud Rate 레지스터

4) UDRn (USART I/O Data Register n)

가) USART I/O 데이터 레지스터 (UDR0, UDR1)

- 1058 -