Page 74 - 2020학년도 MDP과제발표회 자료집 (통신과) (3)

P. 74

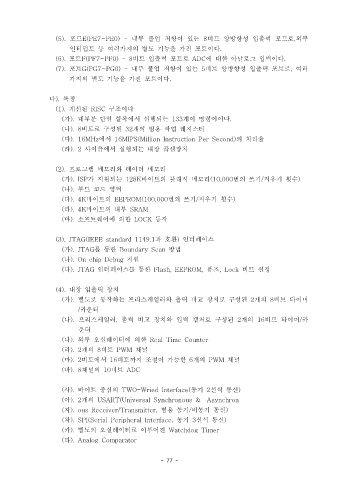

(5). 포트E(PE7~PE0) - 내부 풀업 저항이 있는 비트 양방향성 입출력 포트로 외부 8 ,

인터럽트 등 여러가지의 별도 기능을 가진 포트이다.

(6). 포트F(PF7~PF0) - 8 비트 입출력 포트로 ADC 에 대한 아날로그 입력이다.

(7). 포트G(PG7~PG0) - 내부 풀업 저항이 있는 비트 양방향성 입출력 포트로 여러5 ,

가지의 별도 기능을 가진 포트이다.

다). 특징

(1). 개선된 RISC 구조이다

( 가). 대부분 단일 클록에서 실행되는 133 개이 명령어이다.

( 나). 8 비트로 구성된 32 개의 범용 작업 레지스터

( 다). 16MHz 에서 16MIPS(Million Instruction Per Second) 의 처리율

( 라). 2 사이클에서 실행되는 내장 곱셈장치

(2). 프로그램 메모리와 데이터 메모리

( 가). ISP 가 지원되는 128K 바이트의 플래시 메모리(10,000 번의 쓰기 지우기 횟수/ )

( 나). 부트 코드 영역

( 다). 4K 바이트의 EEPROM(100,000 번의 쓰기 지우기 횟수/ )

( 라). 4K 바이트의 내부 SRAM

( 마). 소프트웨어에 의한 LOCK 동작

(3). JTAG(IEEE standard 1149.1 과 호환 인터페이스)

( 가). JTAG 를 통한 Boundary Scan 방법

( 나). On chip Debug 지원

( 다). JTAG 인터페이스를 통한 Flash, EEPROM, 퓨즈, Lock 비트 설정

(4). 내장 입출력 장치

( 가). 별도로 동작하는 프리스케일러와 출력 비교 장치로 구성된 개의 비트 타이머2 8

/ 카운터

( 나). 프리스케일러 출력 비교 장치와 입력 캡처로 구성된 개의 , 2 16 비트 타이머 카/

운터

( 다). 외부 오실레이터에 의한 Real Time Counter

( 라). 2 개의 비트 8 PWM 채널

( 마). 2 비트에서 16 비트까지 조절이 가능한 개의 6 PWM 채널

( 바). 8 채널의 10 비트 ADC

( 사). 바이트 중심의 TWO-Wried Interface( 동기 선식 통신2 )

( 아). 2 개의 USART(Universal Synchronous & Asynchron

( 자). ous Receiver/Transmitter, 범용 동기 비동기 통신/ )

( 차). SPI(Serial Peripheral Interface, 동기 선식 통신3 )

( 카). 별도의 오실레이터로 이루어진 Watchdog Timer

( 타). Analog Comparator

- 77 -