Page 405 - 완) I MDP 프로젝트 작품 보고서(전체과 1학년)1.6

P. 405

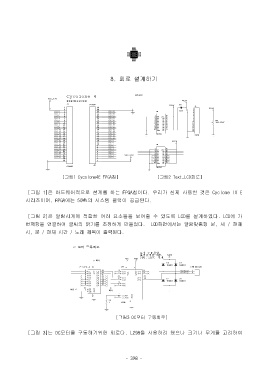

8. 회로 설계하기

Cycolone 4 LCD회회

VCC_3.3V

EP4CE22C8N VCC_5V

J1 CON30 VCC_5V D19

1 30 1 J3 VCC_5V

2 29 2

IO1_0 3 28 IO2_25 U8 DIODE 3

IO1_1 4 27 IO2_24 4 5

IO1_2 5 26 IO2_23 1 20 6

IO1_3 6 25 IO2_22 2 OE VCC 19 7

IO1_4 7 24 IO2_21 3 D0 Q0 18 8

IO1_5 8 23 IO2_20 4 D1 D2 Q1 Q2 17 9 RV2

IO1_6 9 22 IO2_19 5 6 D3 Q3 16 15 10 11 3362P-1-502LF

IO1_7 10 21 IO2_18 7 D4 Q4 14 12

IO1_8 11 20 IO2_17 8 D5 Q5 13 13

IO1_9 12 19 IO2_16 9 D6 Q6 12 14

IO1_10 13 18 IO2_15 10 D7 GND Q7 LE 11 15

IO1_11 14 17 IO2_14 16

IO1_12 15 16 IO2_13 74HC573

IO1_13 16 15 IO2_12 CON16

IO1_14 17 14 IO2_11

IO1_15 18 13 IO2_10

IO1_16 19 12 IO2_9 VCC_5V

IO1_17 20 11 IO2_8

IO1_18 21 10 IO2_7 U9

IO1_19 22 9 IO2_6

IO1_20 23 8 IO2_5 1 20

IO1_21 24 7 IO2_4 2 OE VCC 19

IO1_22 25 6 IO2_3 3 D0 Q0 18

IO1_23 26 5 IO2_2 4 D1 D2 Q1 Q2 17

IO1_24 27 4 IO2_1 VCC_3.3V 5 6 D3 Q3 16 15

IO1_25 28 3 IO2_0 7 D4 Q4 14

29 2 8 D5 Q5 13

30 1 9 D6 Q6 12

10 D7 Q7 11

CON30 J2 74HC573 LE

GND

[그림1 Cycolone4E FPGA칩] [그림2 Text_LCD회로]

[그림 1]은 하드웨어적으로 설계를 하는 FPGA칩이다. 우리가 실제 사용한 것은 Cyclone IV E

시리즈이며, FPGA에는 50㎒의 시스템 클럭이 공급된다.

[그림 2]은 알람시계에 적합한 여러 요소들을 보여줄 수 있도록 LCD를 설계하였다. LCD에 가

변저항을 연결하여 글씨의 밝기를 조정하게 만들었다. LCD화면에서는 알람맞춤형 분, 시 / 현재

시, 분 / 현재 시간 / 노래 제목이 출력된다.

[그림3 DC모터 구동회로]

[그림 3]는 DC모터를 구동하기위한 회로다. L298을 사용하려 했으나 크기나 무게를 고려하여

- 398 -