Page 429 - MDP2020-1

P. 429

················································································ 명장양성프로젝트 【MDP】 과제발표회 자료집 Ⅰ | 423

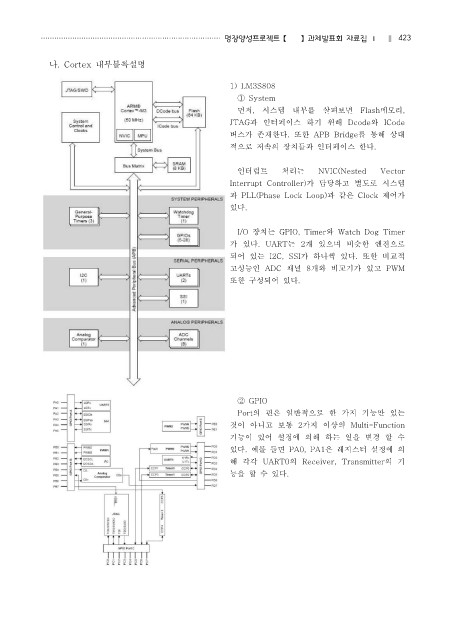

나. Cortex 내부블록설명

1) LM3S808

① System

먼저, 시스템 내부를 살펴보면 Flash메모리,

JTAG과 인터페이스 하기 위해 Dcode와 ICode

버스가 존재한다. 또한 APB Bridge를 통해 상대

적으로 저속의 장치들과 인터페이스 한다.

인터럽트 처리는 NVIC(Nested Vector

Interrupt Controller)가 담당하고 별도로 시스템

과 PLL(Phase Lock Loop)과 같은 Clock 제어가

있다.

I/O 장치는 GPIO, Timer와 Watch Dog Timer

가 있다. UART는 2개 있으며 비슷한 엔진으로

되어 있는 I2C, SSI가 하나씩 있다. 또한 비교적

고성능인 ADC 채널 8개와 비교기가 있고 PWM

또한 구성되어 있다.

② GPIO

Port의 핀은 일반적으로 한 가지 기능만 있는

것이 아니고 보통 2가지 이상의 Multi-Function

기능이 있어 설정에 의해 하는 일을 변경 할 수

있다. 예를 들면 PA0, PA1은 레지스터 설정에 의

해 각각 UART0의 Receiver, Transmitter의 기

능을 할 수 있다.