Page 209 - MDP2020-2

P. 209

················································································ 명장양성프로젝트 【MDP】 과제발표회 자료집 Ⅱ | 203

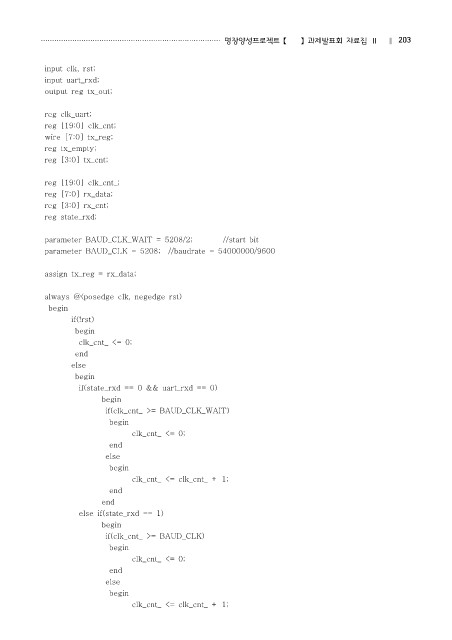

input clk, rst;

input uart_rxd;

output reg tx_out;

reg clk_uart;

reg [19:0] clk_cnt;

wire [7:0] tx_reg;

reg tx_empty;

reg [3:0] tx_cnt;

reg [19:0] clk_cnt_;

reg [7:0] rx_data;

reg [3:0] rx_cnt;

reg state_rxd;

parameter BAUD_CLK_WAIT = 5208/2; //start bit

parameter BAUD_CLK = 5208; //baudrate = 54000000/9600

assign tx_reg = rx_data;

always @(posedge clk, negedge rst)

begin

if(!rst)

begin

clk_cnt_ <= 0;

end

else

begin

if(state_rxd == 0 && uart_rxd == 0)

begin

if(clk_cnt_ >= BAUD_CLK_WAIT)

begin

clk_cnt_ <= 0;

end

else

begin

clk_cnt_ <= clk_cnt_ + 1;

end

end

else if(state_rxd == 1)

begin

if(clk_cnt_ >= BAUD_CLK)

begin

clk_cnt_ <= 0;

end

else

begin

clk_cnt_ <= clk_cnt_ + 1;