Page 182 - 3-2

P. 182

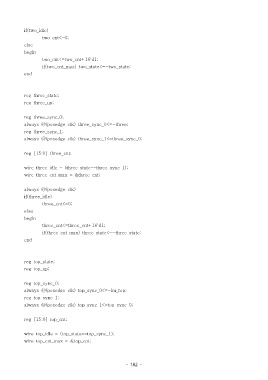

if(two_idle)

two_cnt<=0;

else

begin

two_cnt<=two_cnt+16'd1;

if(two_cnt_max) two_state<=~two_state;

end

reg three_state;

reg three_up;

reg three_sync_0;

always @(posedge clk) three_sync_0<=~three;

reg three_sync_1;

always @(posedge clk) three_sync_1<=three_sync_0;

reg [15:0] three_cnt;

wire three_idle = (three_state==three_sync_1);

wire three_cnt_max = &three_cnt;

always @(posedge clk)

if(three_idle)

three_cnt<=0;

else

begin

three_cnt<=three_cnt+16'd1;

if(three_cnt_max) three_state<=~three_state;

end

reg top_state;

reg top_up;

reg top_sync_0;

always @(posedge clk) top_sync_0<=~lm_top;

reg top_sync_1;

always @(posedge clk) top_sync_1<=top_sync_0;

reg [15:0] top_cnt;

wire top_idle = (top_state==top_sync_1);

wire top_cnt_max = &top_cnt;

- 182 -