Page 788 - 완) I MDP 프로젝트 작품 보고서(전체과 1학년)1.6

P. 788

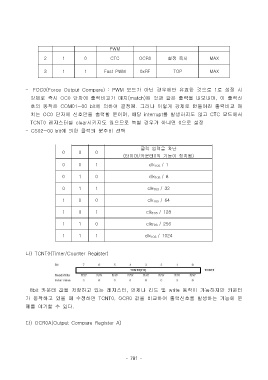

PWM

2 1 0 CTC OCR0 설정 즉시 MAX

3 1 1 F a s t P W M 0 x F F T O P M A X

- FOC0(Force Output Compare) : PWM 모드가 아닌 경우에만 유효한 것으로 1로 설정 시

강제로 즉시 OC0 단자에 출력비교가 매치(match)된 것과 같은 출력을 내보내며, 이 출력신

호의 동작은 COM01~00 bit에 의하여 결정됨. 그러나 이렇게 강제로 만들어진 출력비교 매

치는 OC0 단자에 신호만을 출력할 뿐이며, 해당 interrupt를 발생하지도 않고 CTC 모드에서

TCNT0 레지스터를 clear시키지도 않으므로 특별 경우가 아니면 0으로 설정

- CS02~00 bit에 의한 클럭의 분주비 선택

CS02 CS01 CS00 클럭 소스의 기능

클럭 입력을 차단

0 0 0

(타이머/카운터0의 기능이 정지됨)

0 0 1 c l k TOS / 1

0 1 0 c l k TOS / 8

0 1 1 c l k TOS / 32

1 0 0 c l k TOS / 64

1 0 1 c l k TOS / 128

1 1 0 c l k TOS / 256

1 1 1 c l k TOS / 1024

나) TCNT0(Timer/Counter Register)

8bit 카운터 값을 저장하고 있는 레지스터, 언제나 리드 및 write 동작이 가능하지만 카운터

가 동작하고 있을 때 수정하면 TCNT0, OCR0 값을 비교하여 출력신호를 발생하는 기능에 문

제를 야기할 수 있다.

다) OCR0A(Output Compare Register A)

- 781 -